PCIe 4.0 sẽ có băng thông mỗi lane gấp đôi so với PCIe 3.0, tức ~ 2 GB/s cho mỗi lane cũng như đạt tỉ lệ truyền tải gigatransfer/s đến 16 GT/s với với thiết lập băng thông linh hoạt từ đó mang lại tốc độ truy xuất I/O cao hơn đáng kể, rất hữu ích đối với các loại bộ nhớ lưu trữ, kết nối mạng và ứng dụng AI. Thêm vào đó, PCI-SIG cũng ấn định vào quý 2 năm 2019, họ sẽ công bố cấu hình của PCIe 5.0 thế nên khả năng cao là PCIe 4.0 sẽ không sống lâu như PCIe 3.0 như chúng ta đang dùng. Nhưng đừng lo, PCIe 4.0 sẽ tương thích ngược lẫn xuôi!

PCI-SIG nắm giữ và chuẩn hóa PCIe 1.0 ra mắt năm 2003, PCIe 2.0 năm 2006 và PCIe 3.0 năm 2010. Trả lời trước khoảng thời gian chậm trễ đến 7 năm đối với PCIe 4.0, PCI-SIG cho biết PCIe 3.0 vẫn đang cung cấp đủ băng thông đối với các ứng dụng đang ngày một phát triển và nhu cầu tăng cao như tính toán AI, các loại bộ nhớ PCIe NVMe và 3D Xpoint, tốc độ mạng đặc biệt là 10GbE ngày càng có nhiều người dùng. Đối với nhu cầu xử lý đồ họa của GPU, những giới hạn về băng thông của PCIe 3.0 đã được Nvidia giải quyết bằng việc phát triển liên kết NVLink độc quyền. Với PCIe 4.0 và các phiên bản sau này, PCI-SIG đang tìm cách đưa lộ trình cập nhật này về quỹ đạo thông thường cũng như giải quyết các giới hạn về kỹ thuật để PCIe 4.0 có thể mang lại tốc độ tối đa.

Sự chậm trễ này cũng có lý do bởi bản thân PCI-SIG là một hiệp hội có đến 800 công ty thành viên và mỗi năm, họ đều bầu ra một ban giám đốc mới. Trong nhiệm kỳ 2017 - 2018, thành phần ban giám đốc bao gồm những cái tên như AMD, Intel và Nvidia. Trong việc phát triển và duy trì cấu hình mở của PCI, các công ty thành viên sẽ hoạt động cùng nhau, chia thành các ủy ban và các nhóm phát triển kỹ thuật, từ đó sẽ đệ trình và xem xét những thay đổi về cấu hình của chuẩn PCIe. Sau đó hiệp hội PCI-SIG sẽ tiến hành chuẩn hóa.

Một khi cấu hình được hoàn thiện, các thành viên bắt buộc phải đưa ra các sản phẩm vượt qua được loạt thử nghiệm về 'khả năng tương thích và hợp chuẩn' tại tại một trong những cơ sở chuẩn hóa sản phẩm của PCI-SIG trong suốt cả năm. Sản phẩm đạt yêu cầu sẽ được đưa vào danh sách có thể tích hợp - trong đó các OEM và nhà phát triển hệ thống sẽ sử dụng để chọn phần cứng. Trước khi hoàn thành cấu hình PCIe 4.0 v1 thì chuẩn này đã trải qua nhiều lần chuẩn hóa, gần nhất là phiên bản 0.9 được PCI-SIG cung cấp cho các cơ sở chuẩn hóa của mình cũng như công bố trước các thành viên thuộc hội đồng hồi tháng 6 vừa qua.

Trong đồ thị trên có thể thấy băng thông của PCIe sẽ tăng gấp đôi theo chu kỳ cập nhật. Kể từ khi ra đời, chuẩn PCIe được cập nhật 3 năm một lần rất đều nhưng từ PCIe 2.0 sang PCIe 3.0 thì bắt đầu có chiều hướng chậm trễ. PCIe 1.0 được ra mắt năm 2003 với PCIe 1.0a có băng thông mỗi lane 250 MB/s (x8 đạt 2 GB/s) và tỉ lệ truyền tải 2,5 GT/s, trong năm 2004 thì được nâng cấp về tính năng với PCIe 1.1. Sau 3 năm PCIe 1.0 được thay thế bằng PCIe 2.0 với băng thông mỗi lane tăng gấp đôi lên 500 MB/s (x8 là 4 GB/s và x16 là 8 GB/s), tỉ lệ truyền tải 5 GT/s và cũng từ đây phải mất 4 năm hiệp hội PCI-SIG mới công bố PCIe 3.0.

Chuẩn kết nối phổ biến hàng đầu trên máy tính này được công bố vào tháng 11 năm 2010 sau khi bị trì hoãn nhiều lần với băng thông gấp đôi lên 984,6 MB/s ~ 1 GB/s mỗi lane (x8 là 7,9 GB/s và x16 là 15,8 GB/s), tỉ lệ truyền tải là 8 GT/s. Và giờ với PCIe 4.0, chúng ta đã đợi đến 7 năm để một lần nữa được tận hưởng tốc độ xé gió của PCIe với băng thông mỗi lane 1969 MB/s ~ 2 GB/s (x8 đạt 15,8 GB/s và x16 đạt 31,5 GB/s) và tỉ lệ truyền tải gigatransfer/s là 16 GT/s. Theo những gì PCI-SIG cam kết thì vào năm 2019, PCIe 5.0 sẽ xuất hiện và băng thông dự kiến cũng sẽ tăng gấp đôi theo quy tắc nhưng cấu hình hoàn chỉnh vẫn chưa được tiết lộ.

PCIe 4.0 có tương thích ngược với PCIe 3.0 hay không?

PCIe 4.0 sẽ tương thích ngược với PCIe 3.0 và tương thích 'xuôi' với PCIe 5.0 cả về mặt phần mềm hỗ trợ lẫn giao tiếp cơ học (khe PCIe trên bo mạch) giống như các phiên bản trước. Tức là chúng ta có thể gắn các loại card PCIe 1.x, 2.x và 3.x vào khe PCIe 4.0 mà vẫn hoạt động bình thường. Ngoài ra PCIe 4.0 cũng tiếp tục khai thác kỹ thuật mã hóa 128b/130b của PCIe 3.0.

Ngoài cải tiến về băng thông và tỉ lệ gigatransfer/s thì những cải tiến còn lại mang đến nhiều lợi ích cho các nhà thiết kế và phát triển thiết bị. Một ví dụ, khi tỉ lệ truyền tải giờ đã đạt đến 16 GT/s thì sự biến thiên về hiệu năng sẽ tăng lên và tính toàn vẹn của tín hiệu sẽ giảm. Để giải quyết điều này PCIe 4.0 sẽ đưa công nghệ giới hạn lane xuống tầng vật lý của mô hình OSI (PHY), một ví dụ là chip Ethernet xử lý tín hiệu mạng LAN. Theo đó vi điều khiển PCIe sẽ thu nhận thông tin biên độ điện áp của mỗi lane PCIe để đo dung sai biến thiên. Ngoài ra, PCIe 4.0 còn có các tính năng như 10-bit tag mở rộng và cơ chế điều khiển dòng điện Scaled Flow để khỏa lấp độ trễ và đẩy băng thông lên sao cho luôn ở tốc độ cao nhất. Nhiều cải tiến khác bao gồm giảm độ trễ toàn hệ thống, tích hợp nền tảng và ảo hóa I/O, điều chỉnh tỉ lệ lane/băng thông …

Ứng dụng PCIe 4.0 và những dự đoán:

Ảnh: ExtremeTech.

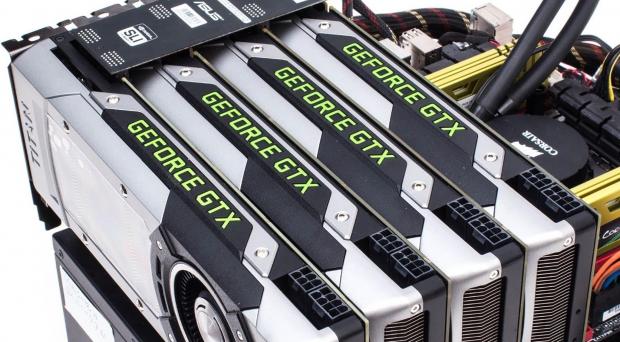

Card đồ họa là một trong những thiết bị tiêu dùng sẽ được lợi từ PCIe 4.0 nhưng với băng thông PCIe bị giới hạn bởi phần lớn CPU dành cho người dùng cuối như 16 lane trực tiếp từ CPU và 4 lane dành cho chipset (DMI 3.0) thì còn rất lâu nữa cơn khát về lane tốc độ cao mới được giải quyết với các thiết lập hệ thống phức tạp gồm nhiều GPU, nhiều ổ SSD NVMe và cả mạng 10GbE.

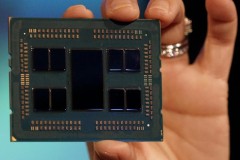

Theo kế hoạch PCIe 5.0 sẽ ra mắt vào năm 2019, như vậy thời gian cho PCIe 4.0 chỉ khoảng 2 năm. Tính đến thời điểm này thì một vài hãng đã bắt đầu phát triển và cung cấp các loại chip PHY 16 GT/s, vi điều khiển, công cụ chuẩn hóa và nhiều phần cứng cho các ứng dụng khác như Synopsy, Cadence, Teledyne Lecroy. Trong khi đó 2 ông lớn làm chip là Intel và AMD cũng đã có lộ trình hỗ trợ PCIe 4.0 nhưng sẽ phải mất vài năm nữa. Chẳng hạn như Intel trước mắt sẽ hỗ trợ PCIe 4.0 dưới dạn một thành phần chặn IP được nhúng thông qua EMIB trên các vi xử lý FPGA dành cho máy chủ mang tên mã Falcon Mesa, tiến trình 10 nm. Về phần AMD, hãng này cũng hướng đến mục tiêu hỗ trợ PCIe 4.0 trên các dòng chip của mình nhưng phải đến năm 2020.

Trước khi sản phẩm được lên kệ thì các bài kiểm tra về khả năng hoạt động và đạt chuẩn cần phải được hoàn tất cùng với các thủ tục/công cụ và cấu hình, rất mất thời gian! Trong cùng thời điểm đó thì PCIe 5.0 với tỉ lệ truyền tải gigatransfer/s đến 32 GT/s cũng đang trên đà nước rút vào năm 2019. Vì vậy sẽ có rất rất ít sản phẩm tiêu dùng dùng PCIe 4.0.

Theo: AnandTech